Når en maskin er programmert, bruker programmøren noen spesielle primitive kommandoer eller maskininstruksjon. Disse kalles vanligvis instruksjonssett på en datamaskin.

Sammenligningstabel

| Grunnlag for sammenligning | RISC | CISC |

|---|---|---|

| Vekt på | programvare | maskinvare |

| inkluderer | Enkelt klokke | Multi-klokke |

| Instruksjonsinnstilt størrelse | Liten | Stor |

| Instruksjonsformater | fast (32-biters) format | Varierende formater (16-64 biter hver instruksjon). |

| Adressemodus brukt | Begrenset til 3-5 | 12-24 |

| Generelle formål registre brukt | 32-192 | 8-24 |

| Minneinferanser | Registrer deg for å registrere deg | Minne til minne |

| Cache design | Del databuffer og instruksjonsbuffer. | Samlet cache for instruksjoner og data. |

| Klokkefrekvens | 50-150 MHz | 33-50 MHz |

| Sykler per instruksjon | Enkeltsyklus for alle instruksjoner og gjennomsnittlig KPI <1.5. | KPI mellom 2 og 15. |

| CPU-kontroll | Hardwired uten kontrollminne. | Mikrokodet med kontrollminne (ROM). |

Definisjon av RISC

RISC-instruksjoner med nedsatt instruksjonsoppsett inneholder vanligvis mindre enn 100 instruksjoner og bruker fast instruksjonsformat (32 bits). Den bruker noen enkle adressemoduser. Register-baserte instruksjoner brukes som betyr at register til registermekanisme er ansatt. LOAD / STORE er de eneste uavhengige instruksjonene for tilgang til minne.

For å øke hastigheten på kontekstbytting, brukes en stor registerfil. Enkelheten av instruksjonssett resulterte i implementering av hele prosessorer på en enkelt VLSI-brikke. De ekstra fordelene er høyere klokkefrekvens, lavere KPI som styrer høye MIPS-karakterer på tilgjengelige RISC / superscalar-prosessorer.

Definisjon av CISC

Kompleks instruksjonssett datamaskiner (CISC) instruksjonssett inneholder rundt 120 til 350 instruksjoner. Den bruker variabel instruksjon / dataformater, men et lite sett med generelle register, dvs. 8-24. Årsaken til store instrukser er bruk av instruksjoner for variabelformat. Et stort antall minnehenvisningsoperasjoner utføres ved å bruke et enormt antall adressemoduser.

CISC-arkitekturen bruker straks HLL-setningene i maskinvare / fastvare. Samlet cache brukes i tradisjonell CISC-arkitektur som inneholder både data og instruksjoner og bruker den vanlige banen.

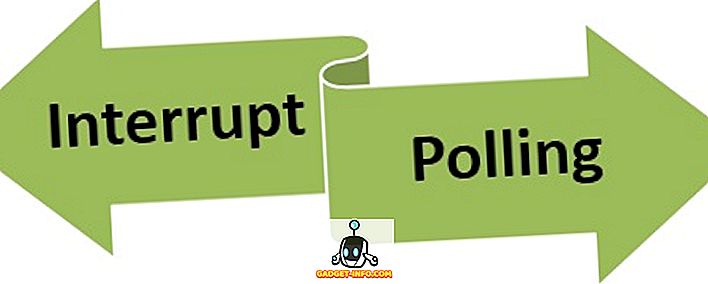

Viktige forskjeller mellom RISC og CISC

- I RISC er instruksjonsinnstillingsstørrelsen liten i CISC, men størrelsen på instruksjonssettet er stor.

- RISC bruker fastformat (32 bits) og for det meste registerbaserte instruksjoner mens CISC bruker variabelformat fra 16-64 bits per instruksjon.

- RISC bruker en enkelt klokke og begrenset adresseringsmodus (dvs. 3-5). På den annen side bruker CISC flere klokke 12 til 24 adressemoduser.

- Antallet generelle formål registrerer at RISC bruker fra 32-192. Tvert imot bruker CISC-arkitekturen 8-24 GPR-er.

- Register-til-register minnemekanisme brukes i RISC med uavhengige LOAD og STORE instruksjoner. I kontrast bruker CISC minne til minnemekanisme for å utføre operasjoner, og innlemmet LOAD og STORE instruksjoner.

- RISC har delt data og instruksjon cache design. I motsetning til, bruker CISC enhetlig cache for data og instruksjoner, selv om de nyeste designene også bruker delt caches.

- Mesteparten av CPU-kontrollen i RISC er hardwired uten å ha kontrollminne. Omvendt er CISC mikrokodet og bruker kontrollminne (ROM), men moderne CISC bruker også hardwired-kontroll.

Konklusjon

CISC-instruksjonene er komplekse og har en tendens til å være langsommere enn RISC, men bruker færre sykluser med færre instruksjoner.